大数据时代对存储器的性能提出了极高的要求,尤其是类脑计算、边缘计算急需功耗极低的存储器。在新型存储器中,相变存储器是与CMOS工艺最兼容,技术最成熟的存储术。 2015年,Intel和Micron推出了傲腾三维相变存储芯片,速度和寿命比固态闪存硬盘要快一千倍,由于其三维堆叠技术容量也高十倍。然而,由于在相变过程中需要将存储介质熔化冷却,导致相变存储器的功耗极高且发热严重,限制了存储容量的进一步增加,也大大增加了其制造成本。目前最先进的数十纳米制程的单个相变存储单元擦写功耗达到了40pJ左右,而实验室制备的百纳米大小的器件功耗达到1000pJ以上。

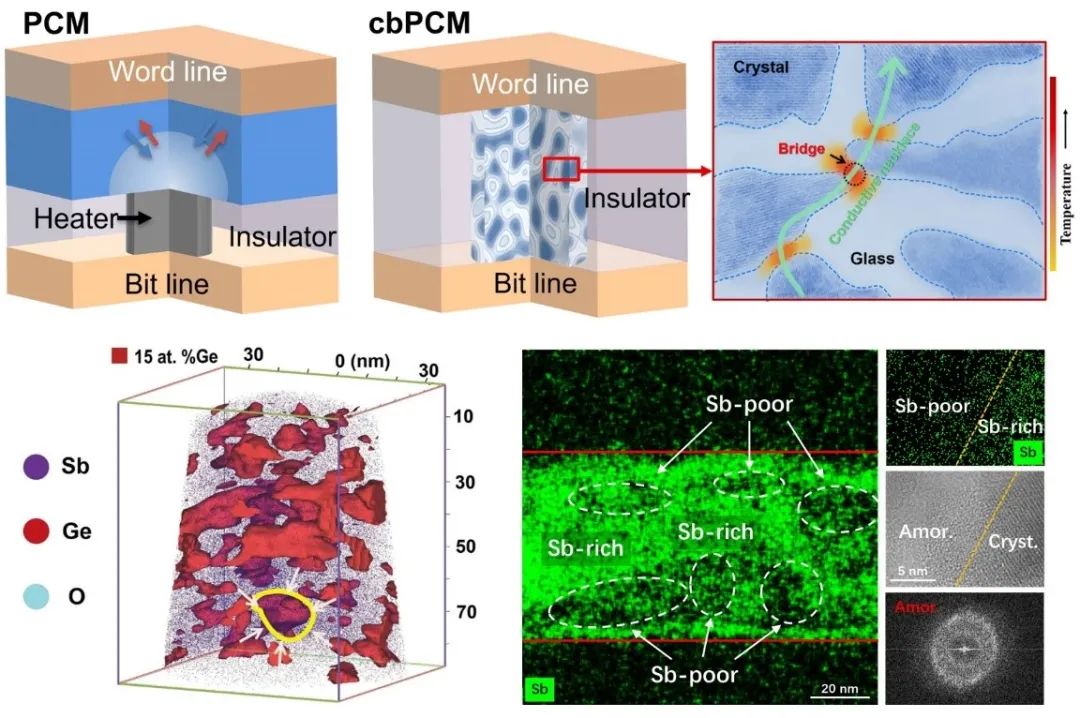

为了解决该问题,华中科技大学信息存储材料及器件研究所(ISMD)联合西安交通大学材料创新设计中心(CAID)研发了一种“导电桥”相变存储器,即设计了新型相变材料锗-锑-氧合金,利用材料的自发分相在存储器件的相变介质层中形成由高阻态非晶网络包围多个低阻态纳米“晶体岛”的异质网络结构。在存储器的操作过程中,异质网络结构基本保持不变,仅通过链接或断开“晶体岛”之间数纳米尺寸的“导电桥”即可实现数据的写入和擦除,极大地减少了相变存储器件的有效相变体积,将数百纳米制程相变存储单元的擦写功耗降低至0.05pJ,与主流产品的功耗相比降低了一千倍,打破了存储器编程过程中功耗与电极/相变介质层接触面积之间成正比的比例关系。“导电桥”相变存储器也保证了较好的一致性和使用寿命。

图:导电桥型相变存储器设计与结构表征

该成果以“超低功耗导电桥型相变存储器设计”(Designing Conductive-Bridge Phase-Change Memory to Enable Ultralow Programming Power)为题发表于《先进科学》 Advanced Science。论文的第一作者为杨哲博士、李博文与王疆靖博士。通讯作者为徐明教授、缪向水教授、张伟教授和马恩教授。该研究是在国家自然科学基金、国家重点研发计划和国家02专项的资助下开展的,原子探针实验受到了中科院上海微系统所朱敏研究员的倾力相助。

论文链接:https://onlinelibrary.wiley.com/doi/10.1002/advs.202103478